Oersjoch fan Semiconductor Process

It semiconductorproses omfettet primêr it tapassen fan mikrofabrykaasje- en filmtechnologyen om chips en oare eleminten folslein te ferbinen binnen ferskate regio's, lykas substraten en frames. Dit fasilitearret de winning fan lead terminals en ynkapseling mei in plestik isolearjende medium te foarmjen in yntegrearre gehiel, presintearre as in trijediminsjonale struktuer, úteinlik foltôging de semiconductor ferpakking proses. It konsept fan it semiconductorproses hat ek betrekking op de smelle definysje fan semiconductor-chipferpakking. Fanút in breder perspektyf ferwiist it nei ferpakkingstechnyk, wêrby't it ferbinen en befestigjen oan it substraat giet, it konfigurearjen fan de oerienkommende elektroanyske apparatuer en it bouwen fan in folslein systeem mei sterke wiidweidige prestaasjes.

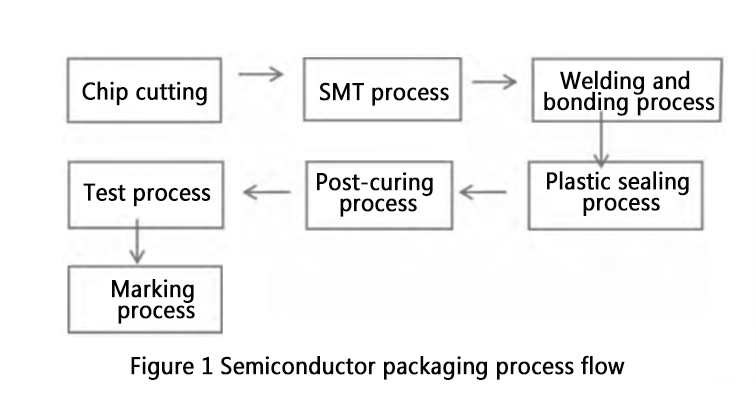

Semiconductor Packaging Process Flow

De semiconductor packaging proses omfiemet meardere taken, lykas yllustrearre yn figuer 1. Elk proses hat spesifike easken en nau besibbe workflows, necessitating detaillearre analyze tidens de praktyske poadium. De spesifike ynhâld is as folget:

1. Chip Cutting

Yn it ferpakkingsproses fan semiconductor omfettet chipsnijen it snijen fan silisiumwafels yn yndividuele chips en it fuortheljen fan silisiumpún om hindernissen foar folgjende wurk en kwaliteitskontrôle te foarkommen.

2. Chip Mounting

It proses foar chipmontage rjochtet him op it foarkommen fan skea oan circuit tidens wafelslijpen troch it oanbringen fan in beskermjende filmlaach, konsekwint de klam op circuityntegriteit.

3. Wire Bonding Process

It kontrolearjen fan de kwaliteit fan it proses foar draadferbining omfettet it brûken fan ferskate soarten gouden triedden om de bondingpads fan 'e chip te ferbinen mei de framepads, en garandearje dat de chip kin ferbine mei eksterne sirkwy en behâld fan algemiene prosesyntegriteit. Typysk wurde dotearre gouden triedden en legere gouden triedden brûkt.

Gedopte gouddraden: Soarten omfetsje GS, GW, en TS, geskikt foar hege bôge (GS:>250 μm), medium-hege bôge (GW: 200-300 μm), en medium-lege bôge (TS: 100-200) μm) respektivelik bonding.

Alloyed Gold Wires: Soarten omfetsje AG2 en AG3, geskikt foar bonding mei lege bôge (70-100 μm).

De diameter opsjes foar dizze triedden fariearje fan 0,013 mm oant 0,070 mm. Selektearje it passende type en diameter basearre op operasjonele easken en noarmen is krúsjaal foar kwaliteitskontrôle.

4. Molding Process

De wichtichste circuitry yn moulding eleminten giet it om ynkapseling. It kontrolearjen fan de kwaliteit fan it mouldingsproses beskermet de komponinten, benammen fan eksterne krêften dy't ferskate graden fan skea feroarsaakje. Dit omfettet in yngeande analyse fan 'e fysike eigenskippen fan' e komponinten.

Trije haadmetoaden wurde op it stuit brûkt: keramyske ferpakking, plestik ferpakking, en tradisjonele ferpakking. It behearen fan it oanpart fan elk ferpakkingstype is krúsjaal om te foldwaan oan wrâldwide easken foar chipproduksje. Tidens it proses binne wiidweidige kapasiteiten nedich, lykas it foarferwarmjen fan 'e chip en leadframe foar ynkapseling mei epoksyhars, foarmjen, en post-mold curing.

5. Post-Curing Process

Nei it foarmjen proses is post-curing behanneling fereaske, rjochte op it fuortheljen fan alle oerstallige materialen om it proses of pakket. Kwaliteitskontrôle is essensjeel om foar te kommen dat it beynfloedzjen fan de algemiene proseskwaliteit en uterlik.

6.Testproses

Sadree't de foarige prosessen binne foltôge, moat de algemiene kwaliteit fan it proses wurde hifke mei avansearre testtechnologyen en -foarsjenningen. Dizze stap omfettet detaillearre opname fan gegevens, rjochte op oft de chip normaal wurket op basis fan syn prestaasjesnivo. Sjoen de hege kosten fan testapparatuer, is it krúsjaal om kwaliteitskontrôle te behâlden yn 'e heule produksjestadia, ynklusyf fisuele ynspeksje en testen fan elektryske prestaasjes.

Testen fan elektryske prestaasjes: Dit omfettet it testen fan yntegreare circuits mei automatyske testapparatuer en garandearje dat elk circuit goed ferbûn is foar elektryske testen.

Fisuele ynspeksje: Technici brûke mikroskopen om de ôfmakke ferpakte chips yngeand te ynspektearjen om te soargjen dat se frij binne fan defekten en foldogge oan kwaliteitsnormen foar semiconductor-ferpakking.

7. Marking Process

It markearringproses omfettet it oerdragen fan de testte chips nei in semi-ferwurke pakhús foar definitive ferwurking, kwaliteitsynspeksje, ferpakking en ferstjoering. Dit proses omfettet trije haadstappen:

1) Electroplating: Nei it foarmjen fan de leads wurdt in anty-korrosjemateriaal tapast om oksidaasje en korrosje te foarkommen. Elektroplatearring technology wurdt typysk brûkt sûnt de measte leads binne makke fan tin.

2) Bending: De ferwurke leads wurde dan foarme, mei de yntegreare circuit strip pleatst yn in leadfoarmjende ark, kontrolearje de leadfoarm (J of L-type) en oerflak-fêstmakke ferpakking.

3) Laser Printing: As lêste, de foarme produkten wurde printe mei in ûntwerp, dat tsjinnet as in spesjale mark foar de semiconductor ferpakking proses, lykas yllustrearre yn figuer 3.

Útdagings en oanbefellings

De stúdzje fan semiconductor ferpakking prosessen begjint mei in oersjoch fan semiconductor technology te begripen syn prinsipes. Folgjende, it ûndersiikjen fan 'e ferpakkingsprosesstream is fan doel om sekuere kontrôle te garandearjen tidens operaasjes, mei help fan ferfine behear om routineproblemen te foarkommen. Yn 'e kontekst fan moderne ûntwikkeling is it identifisearjen fan útdagings yn ferpakkingsprosessen foar semiconductor essensjeel. It is oan te rieden om te konsintrearjen op aspekten fan kwaliteitskontrôle, yngeand behearskje wichtige punten om de proseskwaliteit effektyf te ferbetterjen.

Analysearje út in perspektyf fan kwaliteitskontrôle binne d'r wichtige útdagings tidens ymplemintaasje fanwegen ferskate prosessen mei spesifike ynhâld en easken, dy't elk de oare beynfloedzje. By praktyske operaasjes is strange kontrôle nedich. Troch it oannimmen fan in sekuere wurkhâlding en it tapassen fan avansearre technologyen kinne kwaliteit en technyske nivo's fan semiconductor-ferpakkingsprosessen wurde ferbettere, soargje foar wiidweidige applikaasje-effektiviteit en it realisearjen fan poerbêste algemiene foardielen.(lykas werjûn yn figuer 3).

Post tiid: maaie-22-2024