Applikaasje fjild

1. High-speed yntegrearre circuit

2. Magnetron apparaten

3. Hege temperatuer yntegreare circuit

4. Power apparaten

5. Low macht yntegrearre circuit

6. MEMS

7. Low voltage yntegrearre circuit

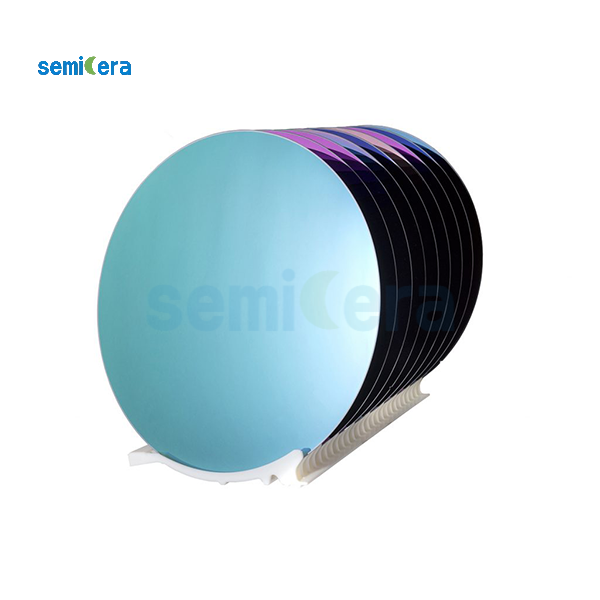

| Ûnderdiel | Argumint | |

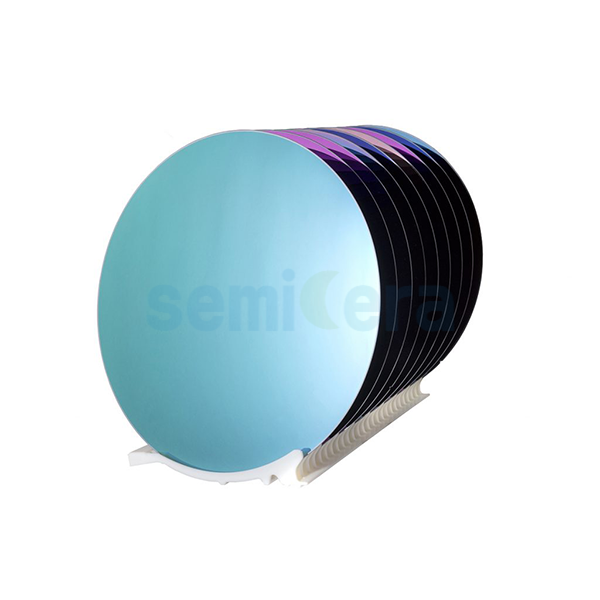

| Overall | Wafer Diameter | 50/75/100/125/150/200 mm±25um |

| Bow/Warp | <10 um | |

| Partikels | 0.3um<30ea | |

| Flats / Notch | Flat of Notch | |

| Râne útsluting | / | |

| Device Layer | Apparaat-laach Type/Dopant | N-Type/P-Type |

| Apparaat-laach Oriïntaasje | <1-0-0> / <1-1-1> / <1-1-0> | |

| Apparaat-laach Dikte | 0.1~300um | |

| Resistiviteit fan apparaat-laach | 0.001~100.000 ohm-cm | |

| Apparaat-laach Particles | <30ea@0.3 | |

| Apparaat Laach TTV | <10 um | |

| Device Layer Finish | Oppoetst | |

| DOAZE | Begraven termyske okside dikte | 50nm(500Å)~15um |

| Handle Layer | Handle Wafer Type / Dopant | N-Type/P-Type |

| Handle Wafer Oriïntaasje | <1-0-0> / <1-1-1> / <1-1-0> | |

| Handle Wafer Resistivity | 0.001~100.000 ohm-cm | |

| Handle wafel dikte | >100um | |

| Handle Wafer Finish | Oppoetst | |

| SOI-wafels fan doelspesifikaasjes kinne wurde oanpast neffens klanteasken. | ||